恀棟抣昞

-

恀棟抣昞丂

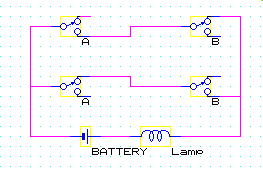

擖椡偵懳偡傞弌椡偺抣傪帵偟偨昞傪恀棟抣昞偲偄偄傑偡丅壓偼丄A偲B偺榓偑婏悢偺偲偒侾偲側傞乮攔懠揑榑棟榓乯偺恀棟抣昞偱偡丅

A B X 侽 0 0 0 1 1 1 0 1 1 1 0

-

僗僀僢僠夞楬傪愝寁偡傞

恀棟抣昞偼夞楬偺巇條彂偵側傝傑偡丅偙偙偱偼丄恀棟抣昞偐傜夞楬傪愝寁偡傞曽朄傪徯夘偟傑偡丅

2曄悢偺応崌

-

愝寁

丂IA偺恀棟抣昞偱丄X偑1偵側傞偵偼丄A偑僆僼偱B偑僆儞偱偁傞応崌丄偁傞偄偼丄A偑僆儞偱B偑僆僼偺応崌偱偡丅

丂偙傟偼丄師偺傛偆側榑棟幃偱昞偡偙偲偑偱偒傑偡丅

丂丂X丂=丂^A丒B丂+丂A丒^B

偙偺幃傪夞楬偱昞偡偲師偺傛偆偵側傝傑偡丅偙偺夞楬偼丄B偺僆儞懁偲僆僼懁傪媡偵偡傞偲丄愭偺奒抜僗僀僢僠偲摨偠夞楬偵側傝傑偡丅偙傟偼丄乽奒抜偺揰摂夞楬乿偲摨偠偱偡丅

3曄悢偺応崌

-

恀棟抣昞偺椺

丂師偺傛偆側3曄悢偺恀棟抣昞傪椺偵峫偊傑偡丅偙偺夞楬偼2恑壛嶼偱丄C傪寘忋偘擖椡偲偡傞偲偒丂A 偲 B丂偺寘忋偘夞楬偵側傝傑偡丅

A B C| X

-----------

0 0 0 | 0

0 0 1 | 0

0 1 0 | 0

0 1 1 | 1

1 0 0 | 0

1 0 1 | 1

1 1 0 | 1

1 1 1 | 1

-

夞楬偺崌惉

丂恀棟抣昞偐傜丄榑棟幃傪嶌惉偡傞偙偲偑偱偒傑偡丅

傑偢丄弌椡偑1偵側傞応崌傪楍嫇偟偰榑棟榓偟傑偡丅忋偺椺偺応崌係庬椶偺擖椡偵懳偟偰X偑1偵側傝傑偡丅嵟弶偺忦審偼丄C丄B偑1偱丄A偑0偺応崌偱偡偐傜丄C丒B丒^A偲側傝傑偡丅懠偺応崌傕摨條偵崌惉偡傟偽丄

丂X=C丒B丒^A + C丒^B丒A + ^C丒B丒A + A丒B丒C

偲側傝傑偡丅偙偺傛偆偵丄榑棟愊偝傟偨崁傪榑棟榓偟偨宍幃傪壛朄昗弨宍偲傛傃傑偡丅

偙偺幃偼

丂A+A=A丂偺惈幙傪棙梡偟偰丄A丒B丒C丂傪晅偗壛偊

丂X=C丒B丒^A +A丒B丒C亄 C丒^B丒A +A丒B丒C亄 ^C丒B丒A + A丒B丒C

椬傝崌偆崁傪丄妵屖偱偔偔傝

丂X=C丒B丒(A+^A)+A丒C丒(^B+B)+A丒B丒(^C+C)

A+^A=1丂傪棙梡偡傞偲

丂X=C丒B +A丒B亄 C丒A

偲娙扨壔偝傟傑偡丅

- 堦斒偺応崌

堦斒偵丄4,5曄悢偺応崌傕丄恀棟抣偐傜丄摨條偵夞楬傪摫偒弌偡偙偲偑偱偒傑偡丅婎杮揑偵偼丄弌椡侾傪弌偡峴傪僗僀僢僠偺捈楍夞楬偱嶌惉偟丄偙偺峴傪暲楍偵愙懕偡傟偽丄椙偄偺偱偡丅偙偺宍幃傪乽偼偟偛宆夞楬丗儔僟乕僒乕僉僢僩乿偲傕屇傃傑偡丅

墳梡丗壛嶼夞楬

-

俀恑悢偲偼

侾寘偺侾侽恑悢偱偼0乣9傑偱偺悢帤偟偐昞尰偱偒傑偣傫丅10埲忋偺悢帤偼擇寘偺悢帤傪棙梡偟偰 10*M+N 傪MN偲昞婰偟傑偡丅俁寘偺悢偼丂LMN丂偲昞婰偟丄

丂丂10*10*L + 10*M + N

傪昞偟傑偡丅

丂摨條偵丄俀恑悢侾暥帤偱偼0,1偟偐昞尰偱偒傑偣傫丅悢丄2,3偼擇寘偺悢帤MN偱

2*M + N 偺傛偆偵昞偡偙偲偑偱偒傑偡丅係埲忋偺悢偼丂3寘偺 LMN丂偱丂2*2*L + 2*M + 2*N 傪昞偟傑偡丅偙傟偱丄0乣7傑偱傪昞尰偱偒傑偡丅

栤戣

6,9,12偵懳墳偡傞2恑悢傪媮傔側偝偄丅

01101丂偵懳墳偡傞10恑悢傪媮傔側偝偄丅

-

2恑悢偺懌偟嶼

2恑悢偺懌偟嶼傕10恑悢偺懌偟嶼偲曄傢傝傑偣傫丅壓偺寘偐傜寘忋偑傝傪峫椂偟偰弴偵寁嶼偟傑偡丅10恑悢偱2埲忋偺応崌偼丄寢壥侾傪師偺寘傊偺寘忋偑傝偲偟傑偡丅- 栤戣

師偺俀恑悢偺壛嶼傪偟丄偝傜偵丄10恑悢偱寁嶼偟偰専嶼偟側偝偄丅

01101+00101=

01001+01111=

- 栤戣

-

n寘偺俀恑悢偺壛嶼

丂n寘偺2恑悢偺壛嶼夞楬傪恀棟抣昞偱掕媊偡傞偙偲傕壜擻偱偡偑寘悢偑懡偔側傞偲尰幚揑偱側偔側傝傑偡丏椺偊偽 5 寘偺壛嶼偺応崌擖椡悢偼10偲側傝傑偡偐傜丆恀棟抣昞偺峴悢偼 1024 偲側偭偰偟傑偄傑偡丏

丂偟偐偟丆恖傕n寘偺壛嶼傪堦搙偵寁嶼偟偰偄傞傢偗偱偼偁傝傑偣傫丅1 寘偺寁嶼傪寘忋偘傪捠偟偰孞傝曉偡偙偲偵傛傝寁嶼偟偰偄傑偡丏懡寘偺 2 恑悢偺壛嶼傕 10 恑偲摨條偵 1 寘偺壛嶼偺孞傝曉偟偱壜擻偱偡丏師偵椺傪帵偟傑偡丏寘忋偑傝傪峫椂偟側偑傜丄壓埵偺寘偐傜弴偵堦寘偯偮寁嶼偟偰偄偔庤弴傪妋擣偟偰壓偝偄丅

丂丂 0 0 1 0

丂+ 0 1 1 0

------------

丂丂1 0 0 0

-

傗傟偽偱偒傞丠

5寘偺壛嶼夞楬傪堦斒揑側曽朄偱愝寁偟傑偡丅擖椡傪丂A4,A3,A2,A1,A0丂偲丂B4,B3,B2,B1,B0丂偲偟傑偡丅擖椡偺悢偑10偱偡偐傜恀棟抣昞乮朰傟偨恖偼慜夞偺恀棟抣昞傪嶲徠乯偺峴偺悢偼丄210=1024丂偲側傝傑偡丅嶌傞尦婥偁傝傑偡偐丠

-

栤戣傪彫偝偔暘夝偟傛偆

丂n寘偺壛嶼婍偼丄堦寘偺壛嶼婍傪師偺傛偆偵丄廲懕偵愙懕偟偰崌惉偡傞偙偲偑偱偒傑偡丅偙偺偲偒丄慜寘偺寘忋偘弌椡D傪師偺寘偺C擖椡偵愙懕偟傑偡丅嵟弶偺寘偺寘忋偘擖椡偼0偲偟傑偡丅

丂弌椡D偼師偺寘偺擖椡C偲側傝傑偡偐傜丄D傪儕儗乕夞楬偵愙懕偟丄C乮丱C乯偼慜偺抜偺儕儗乕D偺僆儞懁乮僆僼懁乯愙揰傪棙梡偟傑偡丅偙偺傛偆偵偡傞偲丄侾寘偺夞楬偑偱偒傟偽偦傟傪n屄暲傋傞偩偗偱丄n寘偺壛嶼夞楬偑偱偒傑偡丅

n寘壛嶼夞楬

栤戣

n=3偲偟偰師偺傛偆偵擖椡傪掕傔偨偲偒丄奺弌椡偺抣傪恾偵婰擖偟側偝偄丅

(A3,A2,A1,A0)=(0,1,1,0)丄 (B3,B2,B1,B0)=(1,0,1,0)

-

侾寘壛嶼夞楬傪愝寁偡傞

侾寘偺壛嶼夞楬傪嶌惉偟傑偡丅傑偢丄X,Y,C 傪擖椡偲偟丄偦偺榓傪S偲偡傞恀棟抣昞傪嶌惉偟傑偡丅師偵丄X,Y,C 傪擖椡偲偟丄偦偺寘忋偘傪D偲偡傞恀棟抣昞傪嶌惉偟傑偡丅S偲D傪寁嶼偡傞僗僀僢僠夞楬傪嶌惉偟傑偡丅S偼儔儞僾偱昞帵偟丄D偼師偺寘偺寘忋偘擖椡C:偵側傝傑偡丅

乮椺乯壛嶼婍偺榓乮S)偲寘忋偘乮D)偺恀棟抣昞

X Y C S D 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

-

敿壛嶼偲慡壛嶼

D偼丄X,Y,C偺擇偮埲忋偑侾偺偲偒1偵側傝傑偡丅偟偨偑偭偰丄

丂D=X丒Y + X丒C + Y丒C

偲側傝傑偡丅

丂X偲Y偲偺攔懠揑榑棟榓傪仢偲偟傑偡丅偡傞偲

丂S=X 仢丂Y丂仢丂C

偲側傝傑偡丅攔懠揑榑棟榓偼敿壛嶼婍偲傕屇偽傟傑偡丅敿壛嶼墘嶼偼擇偮偺怣崋偺榓傪寁嶼偟傑偡偑丄偙傟偼丄攔懠揑榑棟榓偲摨偠偱偡丅X偲Y偺敿壛嶼偵丄偝傜偵C傪敿壛嶼偡傞偲丄乽慡壛嶼乿偵側傝傑偡丅

-

尭嶼夞楬

丂尭嶼夞楬偼俀偺曗悢夞楬傪棙梡偟偰幚尰偱偒傑偡丅X - Y 傪峴偆偵偼丄X 偲 Y 偺 斀揮乮NOT乯傪壛偊丄偝傜偵嵟彫寘偵寘忋偑傝傪壛偊傑偡丅偙傟偱丄丂X + ^Y 亄侾 偺寁嶼偑偱偒傑偡丅偙傟偼丄X 偵 Y偺俀偺曗悢傪壛偊傞偙偲偵側傝傑偡丅

墳梡俀丗斾妑夞楬

-

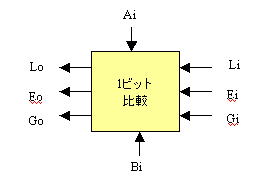

戝偒偝偺斾妑夞楬乮1價僢僩乯

2恑悢偺戝偒偝傪斾妑偡傞夞楬傪嶌惉偟傑偡丅傑偢丄堦寘偺斾妑夞楬傪峫偊傑偡丅A 偲 B傪斾妑偟丄A偑B傛傝彫偝偄偲偒L丄摍偟偄偲偒E丄戝偒偄偲偒 G丄傪侾偲偟傑偡丅

丂E亖A丒B

偼娫堘偄偱偡丅偙傟偱偼丄A=B=0 偺偲偒E=1偵側傝傑偣傫丅惓夝偼

丂E=丱A丒丱B + A丒B

偱偡丅G丄L 偼娙扨偱偡丅

丂G=A丒丱B

丂L=丱A丒B

-

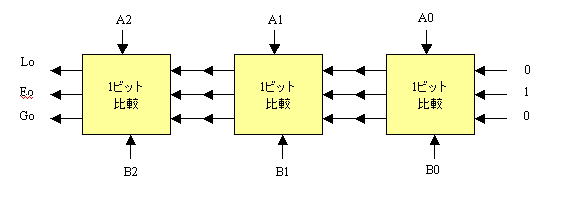

n價僢僩偺斾妑

丂暋悢偺價僢僩傪堦搙偵埖偆偺偼戝曄偱偡丅偙傟傕侾價僢僩偛偲偵暘夝偟偰張棟偟傑偡丅

壓埵偺寘偺 斾妑寢壥傪丂Li丄Ei丄Gi 偲偟丄Ai丄Bi 偺戝彫娭學傪峫椂偟偰丄Lo丄Eo丄Go丂傪弌椡偡傞夞楬傪峫偊傑偡丅偙傟傪丄弴偵廲懕愙懕偡傟偽丄値寘偺斾妑偑偱偒偦偆偱偡

-

墘廗

丂Eo = Ei丒乮Ai=Bi乯

偲側傝傑偡丅偙偙偱丄(Ai=Bi) 偼Ai偲Bi偑摍偟偄偲偒侾偲側傞榑棟幃偲偟傑偡丅

丂Lo 亖( Ai < Bi )丂偲側傝偦偆偱偡偑丄偙傟偩偗偱偼晄廫暘偱偡丅乮Ai=Bi乯偱Li=1 偺応崌傪峫偊傞昁梫偑偁傝傑偡丅

Lo,Go 傪峫偊偰偔偩偝偄丅

-

3價僢僩斾妑夞楬

丂暋悢價僢僩偺斾妑傪峴偆偵偼丄1價僢僩偺斾妑夞楬傪愙懕偟傑偡丅堦斣壓埵偺寘偺斾妑擖椡偼丄L=G=0丄E=1 偲偟傑偡丅嵍偺弌椡偑3價僢僩偺斾妑偺寢壥偱偡丅

壽戣

埲壓偺栤戣傪儗億乕僩梡巻偵傑偲傔曬崘偟側偝偄丅

-

栤戣

師偺恀棟抣昞傪幚尰偡傞榑棟幃偍傛傃僗僀僢僠夞楬傪摫偒側偝偄丅

A B C | X

-----------

0 0 0 | 0

0 0 1 | 0

0 1 0 | 0

0 1 1 | 1

1 0 0 | 0

1 0 1 | 1

1 1 0 | 1

1 1 1 | 1

-

壽戣

1價僢僩斾妑夞楬偺 Lo丄Eo丄Go丄偺榑棟幃傪嶌惉偟側偝偄丅

-

傾儞働乕僩

恀棟抣昞偐傜榑棟幃媦傃夞楬傪崌惉偡傞曽朄偼棟夝偱偒傑偟偨偐丠

丂侾丂偱偒偨丂丂俀 傎傏棟夝偱偒偨丂俁傛偔傢偐傜傫丂丂係慡偔傢偐傜傫

0011 偲 0001 偺懌偟嶼偼偳傟偵側傝傑偡偐

丂侾丏 1001 丂俀丏 100丂丂俁丏111

0011偺俀偺曗悢偼偳傟偵側傝傑偡偐

丂侾丏1100丂丂俀丏1101 丂俁丏1001