婰壇夞楬

-

婰壇夞楬

-

婰壇夞楬偲偼

婰壇慺巕偲偼丄婰壇梡偺怣崋乮S偲偟傑偡乯傪1(0)偵偡傞偲侾傪婰壇偟丄S傪0偵栠偟偰傕1傪曐帩偟傑偡丅0偵栠偡偵偼徚嫀梡偺怣崋傪侾(0)偵偟傑偡丅堦搙乽婰壇乿偡傞偲丄S傪0偵栠偟偰傕婰壇摦嶌傪懕偗傑偡丅偙偙偱偼丄偙偺婰壇夞楬偺巇慻傒偲墳梡偵偮偄偰愢柧偟傑偡丅

-

儔僢僠夞楬

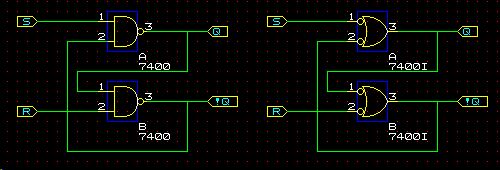

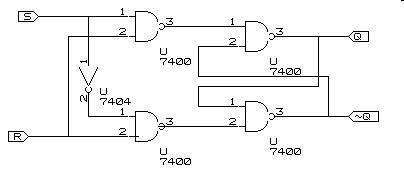

丂僎乕僩夞楬傪慻傒崌傢偣傞偩偗偱丄婰壇夞楬傪嶌惉偱偒傑偡丅師偺擇偮偼摨偠夞楬偱偡丅嵍懁偺夞楬偺慺巕偼NAND慺巕丄塃偼晧擖椡OR慺巕偱峔惉偟偰偄傑偡丅

丂NAND慺巕偼擖椡偑偲傕偵侾偵側傞偲弌椡0傪弌偟傑偡丅晧擖椡OR慺巕偼偄偢傟偐堦曽偺擖椡偑0偺応崌丄弌椡侾傪弌偟傑偡丅擖椡傗弌椡偺仜偑丄侽偲侾偺堄枴傪岎姺乮斲掕乯偟偰偄傞偙偲偵拲堄偟偰偔偩偝偄丅

丂偙偺夞楬偱丄S傪0丄R傪1偵偟傑偡丅S=0 偱偡偐傜 Q 偼侾偵側傝丄!Q 偼0偵側傝傑偡丅偙偺抣 0 偑 A 偺僎乕僩偺懠曽偺擖椡偵擖傝傑偡丅偟偨偑偭偰丄S傪侾偵栠偟偰傕Q偺抣偼曄壔偟傑偣傫丅S亜A.1亜Q亜B.1亜!Q亜A.2丂偲弞娐偟偰偄傞偙偲偵拲堄偟偰偔偩偝偄丅

丂摨條偵R=0丄S=1偵偡傞偲!Q偑侾偵側傝丄Q偼侽偵栠傝傑偡丅R傪侾偵栠偟偰傕Q偼侽偺傑傑偱偡丅偙傟偑丄婰壇夞楬偺尨宆偱丄儔僢僠夞楬偲屇偽傟傑偡丅儔僢僠偼偐傫偸偒乮鑨乯偺堄枴偱丄斷偵朹傪捠偟偰奐暵偱偒側偄傛偆偵偡傞峔憿偱偡丅

- 儕儗乕偱婰壇慺巕偑偱偒傞

杊斊偱巊傢傟傞丄堦搙儃僞儞傪墴偟偰柭傝弌偡偲儃僞儞傪棧偟偰傕柭傝偮偯偗傞夞楬偑偁傝傑偡丅偙傟傕婰壇夞楬偱偡丅

- 幚尡

丂NAND慺巕傪棙梡偟偰儔僢僠夞楬傪嶌惉偟偰偔偩偝偄丅

S傪L乮僌儔儞僪乯偵偡傞偲丄Q偑H乮揰摂乯偵側傞

S,R傪H偵偡傞偲婰壇傪懕偗傞

R傪L偵偡傞偲丄Q偑L偵側傞

S,R傪H偵偡傞偲婰壇傪懕偗傞

偙偲傪妋擣偟偰偔偩偝偄丅

- 壽戣

婰壇夞楬偼儕儗乕傪巊偭偰傕幚尰偱偒傑偡丅偙偺夞楬傪峫偊偰偔偩偝偄丅

僸儞僩

儕儗乕偑ON偵側偭偨傜丄偦偺愙揰偱帺暘偺儕儗乕傪嬱摦偟傑偡丅

-

D宆儔僢僠夞楬

-

儔僢僠夞楬偺栤戣揰

儔僢僠夞楬偺傑傑偱偼婰壇夞楬偲偟偰棙梡偡傞偲偒丄偄偔偮偐偺栤戣揰偑偁傝傑偡丅傑偢丄S,R傪偲傕偵0偵偟偰偟傑偆偲丄婰壇偲徚嫀偑摨帪偵婲偙傞偨傔丄抣偑晄掕乮弌椡偑侽偐侾偐掕傑傜側偄乯偵側傝傑偡丅

-

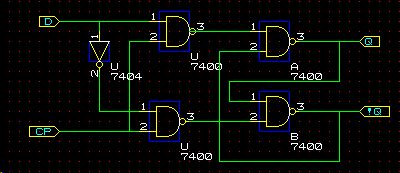

僨乕僞偲僞僀儈儞僌怣崋傪暘棧

偦偙偱丄儔僢僠偺慜偵夞楬傪晅壛偟丄D怣崋偺抣傪CP偺僞僀儈儞僌偱婰榐偡傞傛偆偵偟傑偡丅CP偵僷儖僗乮0>1>0偺怣崋)偑擖傞偲丄D偺抣偵偟偨偑偭偰丄S偲R偵怣崋偑弌傑偡丅偙偺夞楬傪D宆儔僢僠偲屇傃傑偡丅

D偺抣傪丄CP偵僞僀儈儞僌偱乮CP偑1偺娫乯婰榐偱偒傑偡丅

-

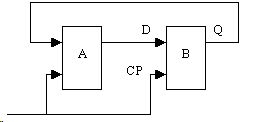

抣偺岎姺偑偱偒傞丠

A,B傪D宆儔僢僠夞楬偲偟偰丄壓恾偺傛偆側夞楬偱抣傪岎姺偟傛偆偲偟偰傕偆傑偔偄偒傑偣傫丅CP偑侾偺娫丄擖椡偼弌椡偵乽撍偒敳偗傞乿偨傔丄A偺擖椡偺抣偑B偵擖傝丄偦傟偑傑偨丄A偵栠偭偰偟傑偄傑偡丅CP傫倫僷儖僗暆偵旝柇側挷惍偑昁梫側側夞楬偵側偭偰偟傑偄傑偡丅

-

僄僢僕僩儕僈宆婰壇夞楬乮FF乯

-

僄僢僕僩儕僈偲偼

僄僢僕偼 帟偲偐抂 偺堄枴偱丄0>1 傗 1>0 傊偺曄壔傪堄枴偟傑偡丅僩儕僈偲偼乽堷偒嬥乿偺堄枴偱丄僄僢僕僩儕僈偼丄怣崋慄偑曄壔偟偨弖娫偵婰壇傪峴偆夞楬偱乮僄僢僕僩儕僈宆乯FF乮僼儕僢僾僼儘僢僾乯偲屇傃傑偡丅婰壇偼堦弖偺娫偵婲偙傝傑偡偐傜丄II偺C

偺傛偆側岎姺夞楬偱傕惓忢偵摦嶌偟傑偡丅

-

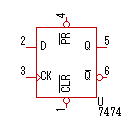

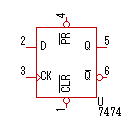

FF慺巕

丂壓偑丄FF慺巕偺僔儞儃儖偱偡丅CK怣崋偺棫偪忋偑傝偱丄D怣崋偺抣傪Q偵婰壇偟傑偡丅PR偲CLR偼儔僢僠婡擻偱丄PR乮僾儕僙僢僩乯傪0偵偡傞偲丂Q=1

丄CLR乮僋儕傾乯傪侽偵偡傞偲 Q=0 偲側傝傑偡丅

-

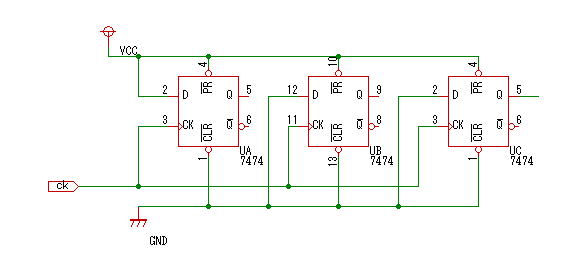

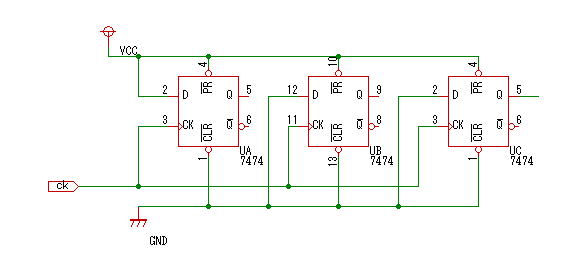

儗僕僗僞

丂FF傪暲傋偰丄暋悢偺怣崋偺抣傪摨帪偵婰壇偡傞夞楬傪儗僕僗僞偲屇傃傑偡丅壓恾偼俁價僢僩偺儗僕僗僞夞楬偱偡丅嵍偺UA偼D傪H乮侾乯儗儀儖丄UB,UC

偼D怣崋傪L乮侽乯儗儀儖偵愙懕偟偰偄傑偡丅偙偙偱丄們倠偵僷儖僗乮0>1偵曄壔偡傞怣崋乯傪壛偊傞偲丄UA,UB,UC 偼丂乮侾丆侽丆侽乯

傪婰壇偟傑偡丅

-

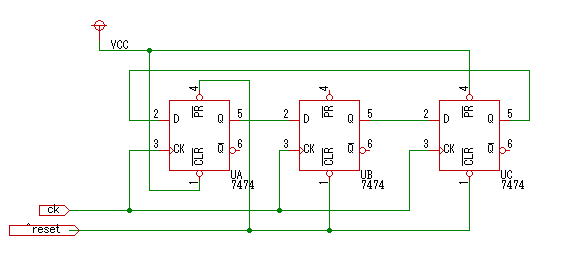

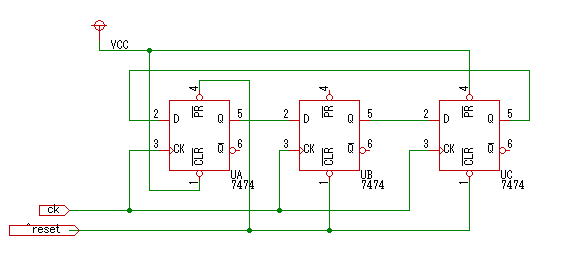

僔僼僩儗僕僗僞

壓恾偼FF3屄傪墶暲傃偵偟偨夞楬偱偡丅^reset 怣崋傪侽偵偡傞偲丄嵟傕嵍偺FF乮UA)傪侾偵丄懡偺FF乮UB,UC乯傪侽偵弶婜壔偟傑偡丅偙偙偱丄ck偵僷儖僗乮0>1偵曄壔偡傞怣崋乯傪壛偊傞偲丄UA偺婰壇抣乮Q)偑UB偺D怣崋偵愙懕偝傟偰偄傞偨傔丄UA偺抣偑UB偵堏傝傑偡丅偳偆傛偆偵丄UB偺抣偑UC丄UC偺抣偑UA丄偵堏摦偟傑偡丅

-

僔儈儏儗乕僔儑儞

-

僔儈儏儗乕僔儑儞

丂僨傿僕僞儖夞楬偼丄摦嶌偑妋掕揑側偨傔丄寁嶼婡僾儘僌儔儉偵傛傞僔儈儏儗乕僔儑儞偑壜擻偱偡丅偙偙偱偼丄CircuitMaker乮惂尷晅偒僼儕乕僂僄傾乯傪棙梡偟偰丄婰壇夞楬偺摦嶌傪僔儈儏儗乕僔儑儞偟傑偡丅

-

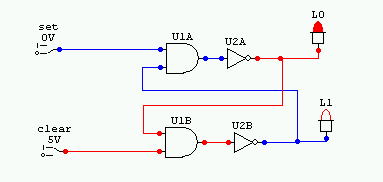

儔僢僠夞楬偺僔儈儏儗乕僔儑儞

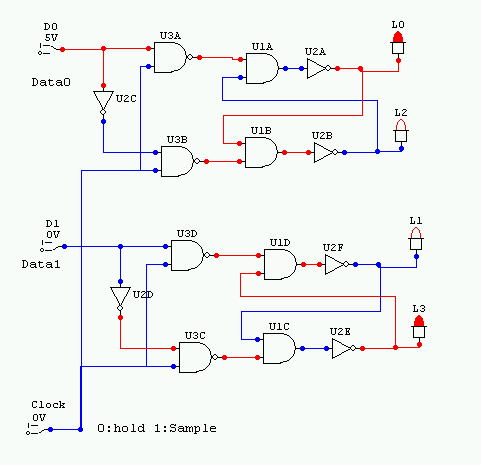

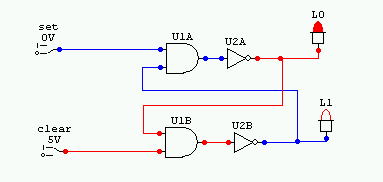

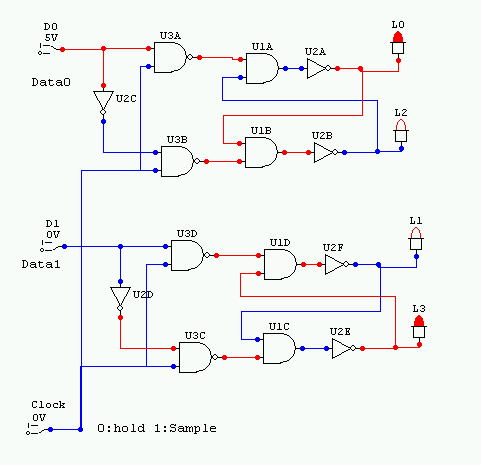

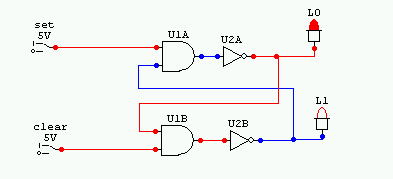

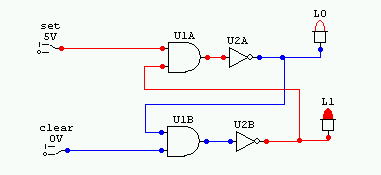

儔僢僠夞楬偺僔儈儏儗乕僔儑儞偱偡丅set懁偺僗僀僢僠傪0丄僋儕傾乮儕僙僢僩乯懁偺僗僀僢僠傪1偵偟偰偄傞偺偱丄L0偼侾傪昞帵偟傑偡丅U1A偲U2A傪愙懕偡傞偲丄NAND慺巕偲摨偠偵側傝傑偡丅

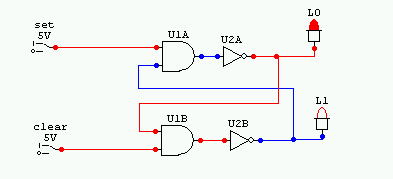

偙偺忬懺偱丄set懁偺僗僀僢僠傪0偵栠偟偰傕丄L0偺忬懺偼曄傢傝傑偣傫丅U2B偐傜偺0怣崋偑丄set偐傜偺0怣崋偑側偔偰傕丄U1A傪0偵屌掕偟偰偄傑偡丅鑨偑偐偐偭偨忬懺偱偡丅set

傪堦搙0偵偡傞偙偲偱丄U2A偵侾偑婰壇偱偒偨偙偲偵側傝傑偡丅

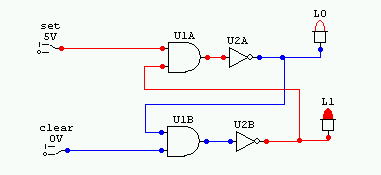

cleal懁偺僗僀僢僠傪0偵偡傞偲丄L0偼0偵側傝婰壇偼僋儕傾偝傟傑偡丅懼傢傝偵L1偑侾偵側傝傑偡丅

-

D宆儔僢僠夞楬偺僔儈儏儗乕僔儑儞

- 儔僢僠夞楬偺栤戣揰

儔僢僠夞楬偺傑傑偱偼婰壇夞楬偲偟偰棙梡偡傞偲偒丄偄偔偮偐偺栤戣揰偑偁傝傑偡丅椺偊偽丄S,R傪偲傕偵0偵偟偰偟傑偆偲丄婰壇偲徚嫀偑摨帪偵婲偙傞偨傔丄婰壇偺抣偑晄掕偵側傝傑偡丅

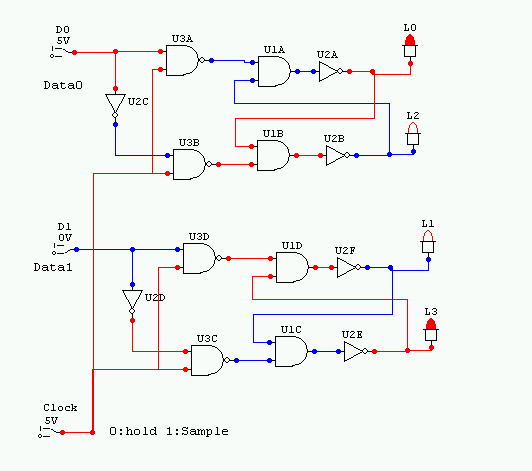

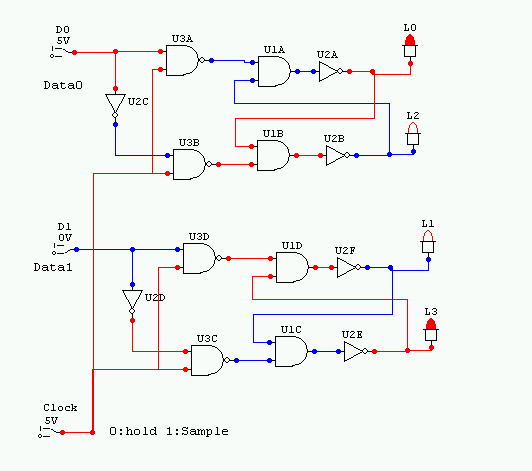

- 僨乕僞偲僞僀儈儞僌怣崋傪暘棧

偦偙偱丄儔僢僠偺慜偵夞楬傪晅壛偟丄D怣崋偺抣傪CP偺僞僀儈儞僌偱婰榐偡傞傛偆偵偟傑偡丅CP偵僷儖僗乮0>1>0偺怣崋)偑擖傞偲丄D偺抣偵偟偨偑偭偰丄S偲R偵怣崋偑弌傑偡丅偙偺夞楬傪D宆儔僢僠偲屇傃傑偡丅

CP偵僷儖僗乮0>1>0偺怣崋)偑擖傞偲丄D偺抣偵Q偵婰榐偟傑偡丅

- 僔儈儏儗乕僔儑儞

丂嵍壓偺Clock僗僀僢僠傪侾偵偡傞偲丄D0偲D1偺僗僀僢僠偺抣傪L0偲L1偵庢傝崬傒傑偡丅

Clock傪0偵偡傞偲丄D0丄D1偺僗僀僢僠傪曄壔偝偣偰傕丄L0,L1偼曄壔偟傑偣傫丅Clock傪0偵偡傞捈慜偺抣偱丄婰壇偼屌掕偝傟傑偡丅