スイッチ回路の欠点

-

速度とサイズ

スイッチ回路は動作は理解しやすいのですが、「遅い、大きい」、等の欠点があります。リレーの動作速度もスイッチよりは高速ですが、速くても1m秒です。半導体(トランジスタ)で構成される最近の集積回路技術で合成された論理回路(ゲート回路と呼びます)の動作速度は1n秒(n:ナノ、10の-9乗)です。大きさも、小型リレーが1cm程度なのに対し、ゲート回路は数μ(マイクロ)mです。

-

単位

ここで、3桁ごとにつけられる数の表現をまとめておきます。

1から3桁単位で大きくすると、

K:キロ、M:メガ、G:ギガ、T;テラ、P:ペタ、E:エクサ

1から3桁単位で小さくすると、

m:ミリ、μ:ミクロン、n:ナノ、p:ピコ、

ゲート回路

-

ゲート回路とは

半導体(トランジスタ)で構成された AND,OR,NOT などの基本的な論理素子をゲート(水門)回路と呼びます。信号を流れと考え、それを制御するのがゲート回路です。

-

MOS型トランジスタ

集積回路(IC)ではスイッチ素子として、トランジスタをスイッチとして利用します。トランジスタにはバイポーラ型とMOS型があります。トランジスタにもMOS型とバイポーラ型の2種類があります。

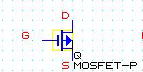

MOS型(左)とバイポーラ型(右)トランジスタの記号

MOSトランジスタは、G(ゲート)、D(ドレイン)、S(ソース)の3端子回路で、Gに正の電圧(数V(ボルト))をかけると、D-S間が導通します。逆に低い電圧の場合、D-S間はオフ(非常に高い抵抗)となります。D-S間がONとなる高い電圧をH、オフとなる低い電圧をLと書きます。

MOSトランジスタはG端子に電圧をかけても電流はほとんど流れません(p(ピコ)A程度の電流)。

-

MOSトランジスタによる論理回路(NAND,NOR)

-

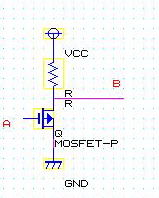

NOT素子

下図はNOT素子です。NOT素子は入力AがH(high:高い電圧)のときトランジスタはONになり出力はGNDに接続するためL(low:低い電圧)になります。入力がLのときトランジスタはオフになり、出力は抵抗を通してVCCに接続するため、Hとなります。入力と出力のレベルが反対になるためNOT素子と呼びます。

-

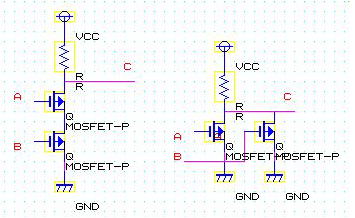

NAND、NOR素子

下図左の素子は,A,B がともにHになると(出力CはGNDに接続するため)出力はLになります。それ以外の入力ではどちらかのトランジスタがオフになるため、出力はHになります。ANDの出力にNOTを付けた回路動作になるため、NOT-AND ですが、これをまとめてNAND素子と呼びます。。

右の素子は、A,Bいずれか一方がHのとき、出力がLになります。ORの出力にNOTを付けた回路動作になるためNOR素子と呼ばれます。NAND、NOR素子の後ろにNOTを接続すれば、AND、OR素子になります。

-

問題

NANDとMOR素子の真理値表(すべての入力に対する出力の表)を作成しよう。

-

ゲート回路の組み合わせ

-

ゲート素子の記号

左から、NAND,NOR,NOT素子の記号です。その右は、NAND、NOR素子の出力をさらに反転した出力をするAND,OR素子です。○ が0と1の逆転(否定)を意味しています。端子の番号はICのピン番号です。詳細は実験の項で説明します。

-

AND、OR、NOTの組み合わせ回路

すべての回路は(否定付きの)論理変数の論理積の和で表現されますから、NOT、AND、ORを組み合わせると、任意の組み合わせ回路を合成することができます。

A・^B + ^A・B の回路

この形式の回路は、ANDとORをNANDで置き換えても同じ動作をします。これは、排他的論理和になります。ANDとORをNANDで置き換えると、等価な回路になります。

-

問題ヒント

上の二つの回路が同じ動作をする(入力が同じなら、出力が同じ)ことを確認しなさい。

「ヒント」

二つのNAND素子の間に図に用にNOT素子を二つつけても無害です。各NOTを左右のNAND素子にくっつけてみよう。

-

一般回路の合成

AND,OR,NOT素子を用いて論理式をそのままゲート回路にすることができます。論理積の論理和の形式で設計された回路は、NANDの2段回路で合成することができます。

演算回路とシミュレーション

-

加算回路

ゲート回路で加算回を設計します。1ビットの加算回路を設計すれば、これを接続することで、任意桁の加算回路を設計できます。1桁の加算回路は、桁上げを含めた加算回路と、桁上げ作成回路から構成されます。

各桁の加算信号を X,Y 、桁上げ信号をC とすると、加算は

S=X ◎ Y ◎ C

となります。◎ は排他的論理和で、どちらか1方のみが1のとき、出力1とする演算です。

また、桁上げはX,Y,C の内、最低二つの信号が1となるとき、出力1となりますから、

C=X・Y + X・C + Y・C

となります。

-

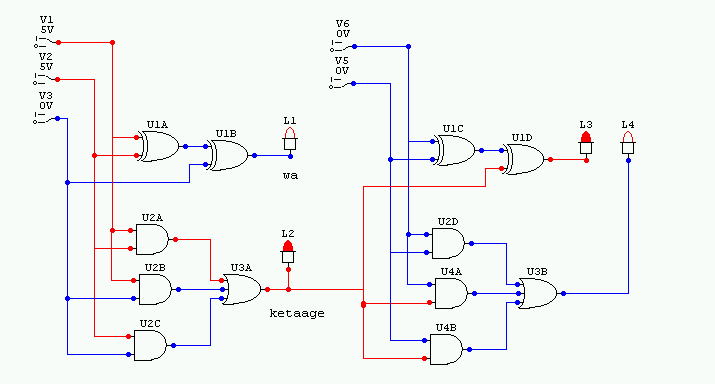

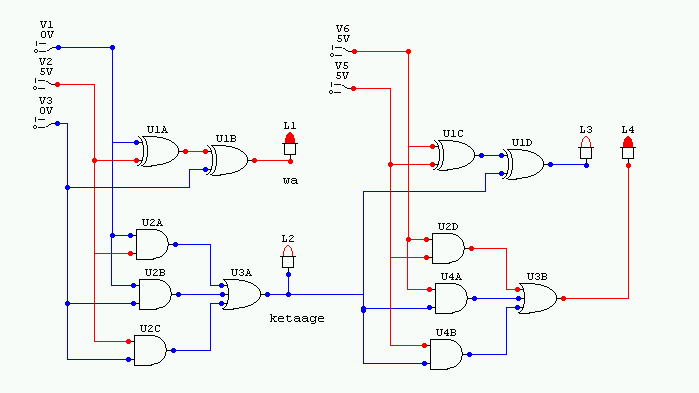

シミュレーション(デモ)

論理回路は CircuitMaker を利用して入力し、シミュレーションすることができます。下は2桁の加算回路です。左上に、第1桁の加算入力と桁上げのスイッチ、中央上に第2桁の入力用のスイッチがあります。回路で赤色の信号は状態が1(Hレベル)、青の信号は0(Lレベル)を意味しています。図では、第1桁の加算入力が(1,1)で桁上がり0、第2桁の加算入力が(0,0)の状態です。中央下の桁上がり信号が1になり(ランプも点灯しています)、これが第2桁に入るため、2桁の加算結果は1になっています。結果として (L4,L3,L1)=(0,1,0) となり、十進数では2となります。

下の図は、第1桁の加算入力が(0,1)で桁上がり0、第2桁の加算入力が(1,1)の状態です。第1桁の桁上がりは0ですが、第2桁の桁上がりが1となり、結果として (L4,L3,L1)=(1,0,1) となり、十進数では5となります。

TOPICS

-

NANDは万能素子(参考)

NANDの2つの入力に同じ信号を入れるとNOT素子になります。NANDの後ろにNOTを付けるとAND素子になります。ドモルガンの定理を応用すると、ORはANDで合成できますから、NAND素子のみですべての論理を合成することができます。

したがって、NAND素子があれば、NOT,AND,ORができますから、NAND素子のみで任意の回路が合成できます。このような素子を「万能素子」といいます。 -

排他的論理和

排他的論理和は階段スイッチでもお馴染みです。どちらか片方のみが1のとき1となりますが、共に1のときは0になります。共に1のとき1となるので、「排他的:exclusive」と呼ばれます。

実は、通常の代数では 排他的ORを 加算とします。普通のORを加算(+演算)とすると、

1 + 1 = 1 + 0

ですから、双方にある1を削除すると、1=0 となる不具合が発生します。

演習

次の論理式をゲート回路で合成しなさい。

A・^B + ^B・C

^(A + B)・(A + ^C)

上の論理式をNAND素子のみで合成しなさい。