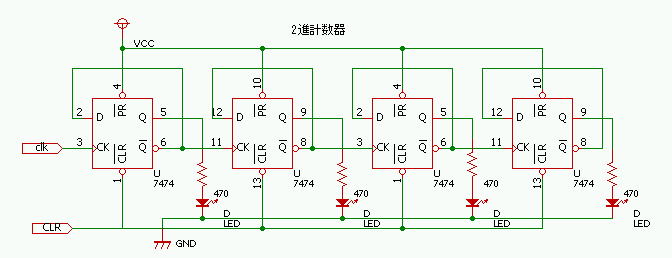

寁悢夞楬

-

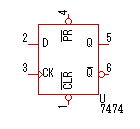

D宆FF慺巕

丂FF偼僋儘僢僋怣崋偺僄僢僕乮曄壔乯偱丄D怣崋偺抣傪婰壇偡傞婰壇慺巕偱偡丅婰壇抣偼Q偵丄偦偺斀揮偟偨抣傪丱Q偵弌椡偟傑偡丅

CLR怣崋傪0偵偡傞偲丄Q傪僋儕傾(0)偲偟丄PR傪0偵偡傞偲丄Q傪僾儕僙僢僩(1)偵偟傑偡丅 -

2恑寁悢婍偺栶妱

2恑僇僂儞僞偼擖椡偲側傞怣崋偺僷儖僗偺悢傪2恑悢偱寁悢偟傑偡丅寁悢婍偼慜偺悢偵1傪壛嶼偡傞摿庩側墘嶼婍偱偡丅偙傟傑偱偺寢壥傪婰壇偡傞偨傔偺婰壇婡擻偑昁梫偱偡丅2恑悢偺曄壔傪挷傋偰傒傑偡丅

4 2 1

---------

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

戞堦寘偼慜偺抣傪斀揮偟偰偄傑偡乮0偐傜1丄傑偨偼丄1偐傜0偵曄壔偡傞乯丅俀偺寘偼丄侾偺寘偑1偐傜0偵曄壔偡傞偲丄斀揮偡傞偙偲偑傢偐傝傑偡丅傑偨係偺寘偼丄俀偺寘偑1偐傜0偵曄壔偡傞偲丄斀揮偡傞偙偲偑傢偐傝傑偡丅偟偨偑偭偰丄慜偺寘偑 1>0 偵曄壔偡傞偲丄帺暘偺抣傪斀揮偡傟偽傛偄偙偲偵側傝傑偡丅

丂偙傟偼丄10恑悢偱偼丄慜偺寘偑9偐傜0偵栠偭偨応崌丄師偺寘偑1偮憹偊傞偙偲偵憡摉偟傑偡丅 -

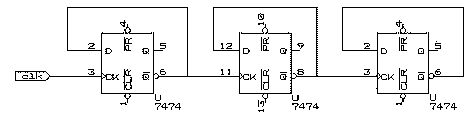

3bit2恑寁悢婍

丂寁悢夞楬偼丄D宆FF傪棙梡偟偰師偺傛偆偵嶌惉偱偒傑偡丅抣傪斀揮偡傞偵偼 丱Q 傪 D 偵擖椡偟傑偡丅偙偺忬懺偱 CLK 偵僷儖僗傪擖傞偲丄Q 偺抣偑斀揮偟傑偡丅Q 偑 1 偐傜 0 偵曄壔偡傞偲丄丱Q 偼 0 偐傜 1 偵曄壔偟傑偡丅偟偨偑偭偰丄慜偺抜偺 ^Q 傪師偺抜偺 CK 偵愙懕偡傟偽丄寘忋偑傝偑峴傢傟傞偨傔寁悢婍偲偟偰摦嶌偟傑偡丅

-

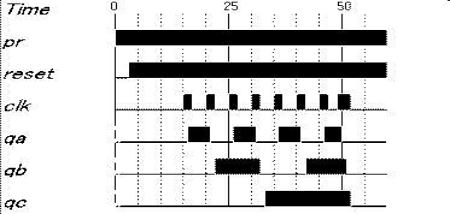

僞僀儉僠儍乕僩偲榑棟僔儈儏儗乕僔儑儞

墶幉偵帪娫傪丄廲曽岦偵奺怣崋偺榑棟抣偺曄壔傪帵偟偨恾傪僞僀儉僠儍乕僩乮帪娫恾乯偲偄偄傑偡丅榑棟僔儈儏儗乕僞偼丄夞楬恾偲擖椡怣崋偺曄壔偐傜奺怣崋偺曄壔傪挷傋丄僞僀儉僠儍乕僩傪弌椡偟傑偡丅擖椡偑曄壔偟偰偐傜丄扨埵帪娫抶傟偰弌椡偑曄壔偟偰偄傑偡丅偙偺帪娫偼慺巕偺摦嶌帪娫偵憡摉偟傑偡丅

墶幉偵帪娫傪丄廲曽岦偵奺怣崋偺榑棟抣偺曄壔傪帵偟偨恾傪僞僀儉僠儍乕僩乮帪娫恾乯偲偄偄傑偡丅榑棟僔儈儏儗乕僞偼丄夞楬恾偲擖椡怣崋偺曄壔偐傜奺怣崋偺曄壔傪挷傋丄僞僀儉僠儍乕僩傪弌椡偟傑偡丅擖椡偑曄壔偟偰偐傜丄扨埵帪娫抶傟偰弌椡偑曄壔偟偰偄傑偡丅偙偺帪娫偼慺巕偺摦嶌帪娫偵憡摉偟傑偡丅

丂忋偐傜丄FF偺僾儕僙僢僩丄reset丄clk丂怣崋偱偙傟偼僔儈儏儗乕僞傊偺擖椡偵側傝傑偡丅qa,qb,qc丂偑奺FF偺弌椡偱僔儈儏儗乕僔儑儞偟偨寢壥傪昞帵偟偰偄傑偡丅 -

僋儕傾丒僾儕僙僢僩夞楬

2恑寁悢夞楬偺応崌丄僾儕僙僢僩偼晄梫側偺偱怣崋傪1偵屌掕偟傑偡丅僋儕傾怣崋偼丄寁悢婍偺忬懺傪0偵偡傞応崌棙梡偟傑偡丅

幚尡夞楬

-

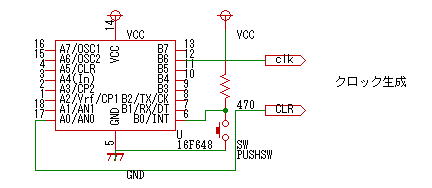

僋儘僢僋夞楬

丂偙偙偱偼丄PIC乮彫宆慻傒崬傒僐儞僺儏乕僞乯傪梡偄偰丄僋儘僢僋傪惗惉偟傑偡丅B1乣B7 抂巕偼僋儘僢僋傪惗惉偟傑偡丅B6抂巕偑1夞/昩偺僷儖僗丄B5偼B6偺丄B4偼B5偺攞偺懍偝偺僋儘僢僋傪惗惉偟傑偡丅

B0偵僗僀僢僠傪愙懕偡傞偲丄僗僀僢僠傪墴偡偲A0偵扨敪偺僷儖僗傪惗惉偟傑偡丅偙傟偼丄僇僂儞僞偺弶婜壔偵棙梡偟傑偡丅 -

幚尡夞楬

丂幚尡梡偺2恑僇僂儞僞偱偡丅IC偼丂7474 傪棙梡偟傑偡丅PR偼H(1儗儀儖)偵屌掕偟傑偡丅CLR偼墴偟儃僞儞偐傜偺怣崋偱寁悢抣傪弶婜壔偟傑偡丅奺寘偺FF傪LED偵愙懕偟丄抣傪妋擣偟傑偡丅

-

岆摦嶌

丂PR偺怣崋傪H乮俆V乯偵屌掕偟側偄偱丄柍愙懕偺忬懺偵偟偰傒偰偔偩偝偄丅寁悢摦嶌偑偲偒偳偒幐攕偟傑偡丅偙傟偼丄僲僀僘偵傛傝FF偑僾儕僙僢僩偝傟偰偟傑偆偐傜偱偡丅