CMOSゲート回路

-

NMOSゲート回路

-

NMOS回路

CMOS回路の前に基本となるNMOS回路を説明します。

-

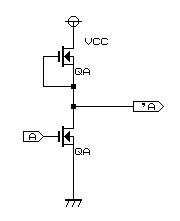

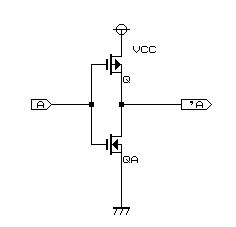

NOT回路

AがHレベルになると、QAが導通して、'A がLレベルになります。VCC側に接続しているトランジスタQAは単に抵抗として利用しています。

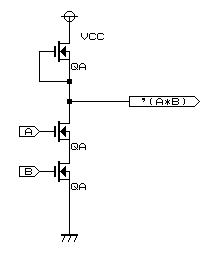

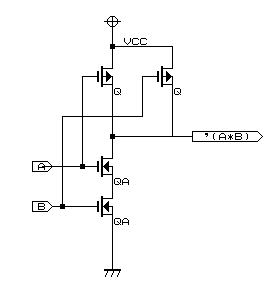

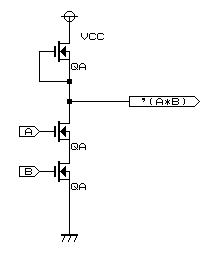

- NAND回路

A,BともにHレベルとなると、出力はLレベルになります。

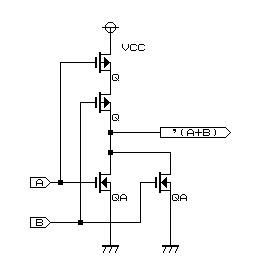

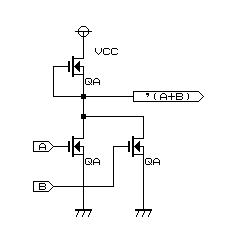

- NOR回路

-

CMOSゲート回路

- CMOS回路

NMOS回路は、出力がLのとき負荷抵抗で電力を消費します。CMOS回路はこの電力を軽減する目的で設定されました。負荷抵抗の替わりに、N型で作成していた論理の逆の回路をP型MOSで作成します。

上部のP型回路がHを出力すると、下部のN型回路はオフになるため、電源からの電流は流れません。出力も次段のゲートに接続するため、流れる電流は

n(ナノ)A 程度しか流れません。

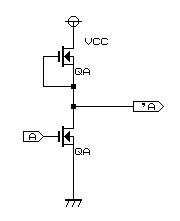

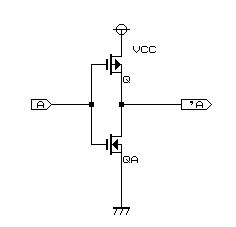

- NOT回路

AがHになると、下のQAがオン、上のQはオフになり、出力はLになります。AがLになると、逆になります。

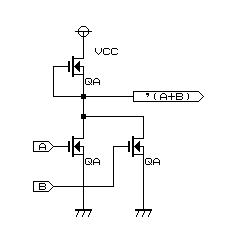

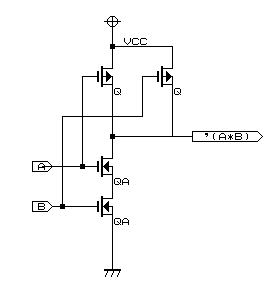

- NAND回路

下のN型の回路はAND(直列)接続です。上のP型回路はOR(並列)接続と逆回路を構成します。

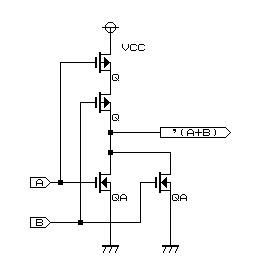

- NOR回路

N型の回路がOR(並列)接続ですから、P型はAND(直列)接続とします。