- シリコンと半導体

シリコンは外周に4個の電子を持つ原子で、純粋のシリコン結晶はこの4個の電子を共有する形で安定しており、電子の移動はありません。したがって絶縁体となります。

このシリコンに、微量のリンを加えると、リンの外周には5個の電子があるため余った電子は、外部からの電解で移動が容易です。この状態をN型半導体といいます。

また、ボロンを加えると、これは外周に3個の電子を持つため電子のない結合が生まれ、この部分を埋めるように電子が移動可能となります。この状態をP型半導体といいます。P型半導体は電子のない場所の移動となるため、等価的に+の電子が移動すると考えることができます。

- PN接合とダイオード

ピンクのP型半導体と緑のN型半導体を接合し電圧をかけます。P型に+、N型に-を印可すると、P型の+電子は反発してN型の方に、N型の自由電子はP型の方に移動し、持続的に電流が流れます。

しかし、逆方向に電圧をかけると、P型の+電子は右に、N型の-電子は左に移動し、中間に電子のない領域が忌まれ、電子は流れません。絶縁状態になります。これがダイオードの原理です。

- MOS型トランジスタ

N型のMOS型トランジスタは、弱いP型の半導体の両側をN型とし、中央に絶縁層を介して、電極Gをつけます。このままでは D-S 間に電圧をかけても、一方が逆電圧になるため、電流が流れません。

しかし、G電極に +電圧をかけると、ゲート電極の下の表面(チャネル部と呼びます)に電子が誘起され、この電子がDの+電圧に流れ込みます。同時にSからゲートに電子が流れ込むため、電流が流れます。

G電圧により誘起される電子に比例した電流が流れることになります(これを応用したのが、低電流ダイオードです)。ゲート部にごく微量のN型不純物を打ち込んでおくと、ゲート電圧が0でも電流が流れます。この状態をデプレッション型と呼びます。

- 霧吹き

IC(集積回路)の作成プロセスは、「型紙」と「霧吹き」によるパターン作成に類似しています。型紙に配線パターンの部分を切り抜き、霧の替わりにアルミを蒸着します。これで、平面上に配線パターンが作成されます。

半導体はシリコンチップ上に、リンやボロンなどの不純物を適量加えることで、生成されます。不純物を加える場所を制御するため、「型紙」が利用されます。

シリコンチップの全面に SiO2 などの絶縁膜を生成します。つぎに、「型紙」を不純物を入れる場所のみ SiO2 を除去して穴をあけSi を露出します。次に不純物のガスを導入して、穴の部分に不純物を埋め込みます。

このような操作を繰り返すことで、Si の表面に半導体を作成し、これらの部品の間を アルミの蒸着膜で接続します。

- 超小型のIC部品

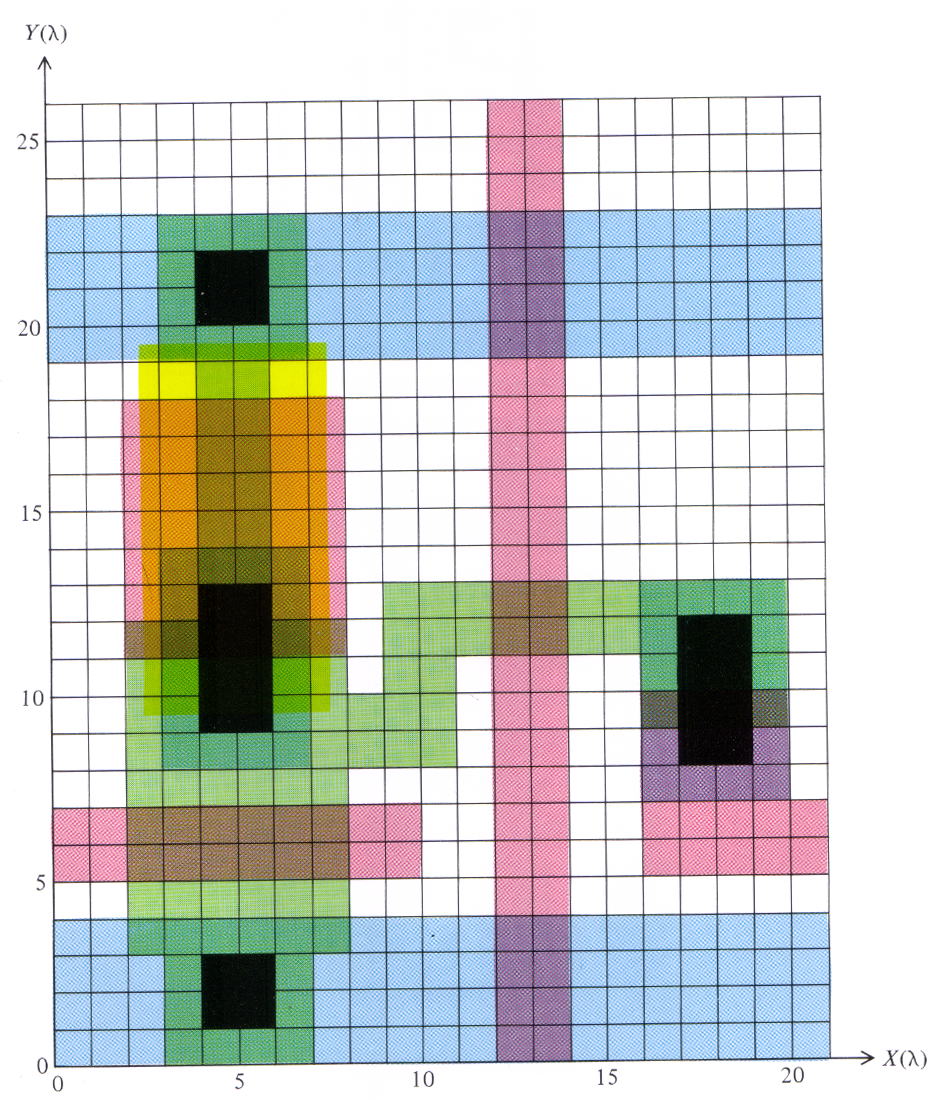

型紙をマスク、型紙の切り抜き形状をマスクパターンといいます。現在、マスクの作成精度はサブミクロンの単位です。論理回路を構成するトランジスタは ミクロン の幅で作成されます。したがって、1mmの幅に1000個のトランジスタが並びます。これを2次元に敷き詰めると、1000*1000 で100万個のトランジスタを収容できます。

実際には、素子と同程度の配線領域が必要ですから、トランジスタの密度は減りますが、現在の大型の集積回路は、数千万のトランジスタで構成されています。

これを作成するためには、ミクロン以下の精度のマスクパターンと各マスクを誤差なく重ね合わせる技術が必要です。

- NOT回路のパターン

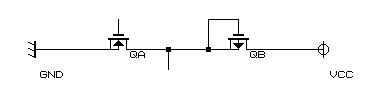

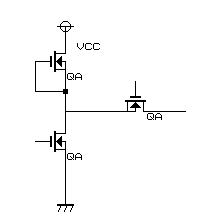

下図のようなMOSトランジスタによるNOT素子を作成するためのパターンを紹介します。QAがエンパンスメント型MOSトランジスタ(VGS=0のときオフ)、QBはデプレッション型トランジスタでVGS=0 でもある程度の電流がながれるため、抵抗の替わりに利用しています。

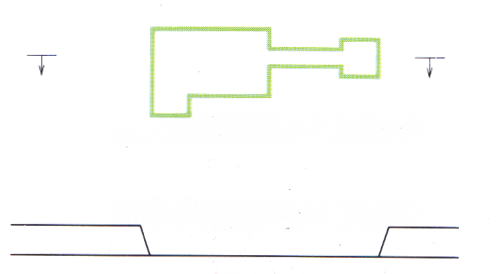

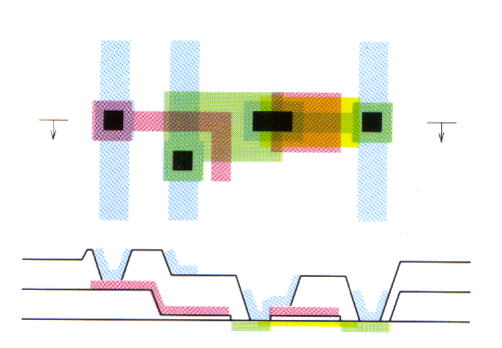

- トランジスタ部以外をマスクする

まず、前面を SiO2(絶縁膜)で覆い、トランジスタ部のみ開口します。上の図画平面図、下が断面図です。断面図の位置は、平面図の中央の部分で、矢印でマークされた部分です。

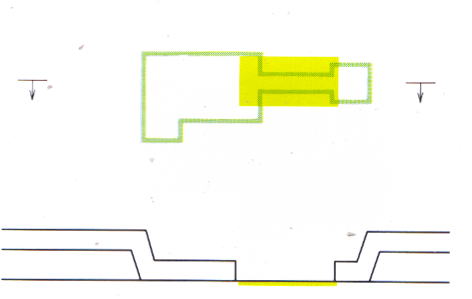

- 負荷トランジスタ部

右側のQBのゲート部に、わずかの不純物を打ち込み、デプレッション型とするための穴をあけます(図の黄色の部分)。この穴に、制御された量の不純物を打ち込みます。

ゲート部が細長く延びているのは、デプレッション型MOSの抵抗の値を大きくするためです。

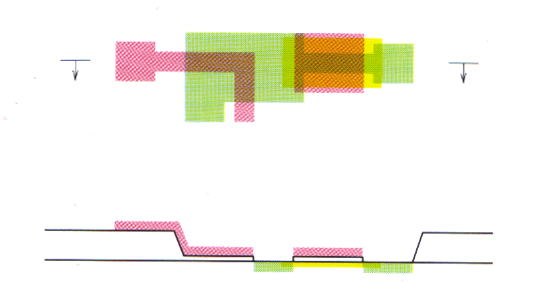

- 拡散領域

次に、全面をSiO2で覆って絶縁した後、全面にポリシリコンを成長させた後、ピンクの部分以外のポリシリコンを除去します。ポリシリコンは多結晶型のシリコンで、導電性の薄膜となります。この場合、ポリシリコンはゲート電極の役割を果たします。

このポリシリコンの上から、緑の部分に穴を開けn型不純物を拡散させます。これで、二つのトランジスタが生成されます。ポリシリコンで分離された緑の部分が、ソースとドレインになります。

- コンタクト部

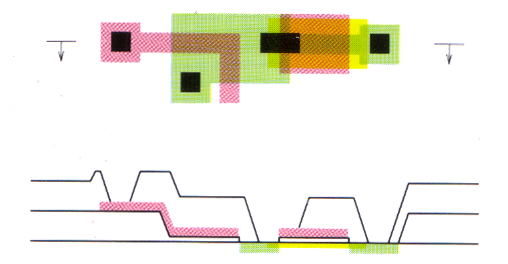

- メタル蒸着による配線

全体をSiO2で絶縁した後、電極となる黒い部分に穴をあけ、全面にアルミを蒸着した後、青色の部分以外のアルミを除去します。これで、配線パタンが作成されます。アルミがポリシリコン(ゲート)や拡散(ドレイン、ソース)を接続していることに注意して下さい。

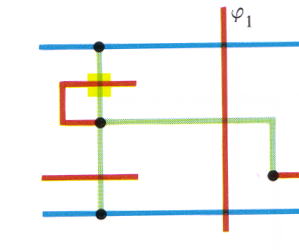

シンボル表記の回路を一度スチック表現すると、マスクパターンとの関係がわかりやすくなります。

下が、スチック表現で、緑の拡散と赤のポリシリコンが交差した位置にトランジスタが生成されます。水色がアルミ配線、赤がポリシリコンの配線です。赤と水色の配線は立体交差しますから、黒色のコンタクトがなければ、交差しても接続することはありません。

このスチック図から下のマスクパターン図を生成します。黄色、ピンク、緑、黒、水色、の5層のマスクパターンを重ね合わせて、表示しています。

(パターン図はすべて、ミード著:超LSI:培風館 からの引用です)