婰壇夞楬

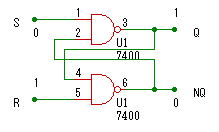

丂NAND慺巕傪2屄棙梡偟丄偟偨偺傛偆偵寢慄偡傞偲丄婰壇夞楬偑幚尰偱偒傑偡丅

S偲R偼捠忢侾偵偟偰偍偒傑偡丅S偺抣傪0偵偡傞偲丄3抂巕乮Q乯偼侾偵側傝傑偡丅俁抂巕偼壓偺NAND偺擖椡偵側傝丄俆抂巕偼侾偱偡偐傜丄俇抂巕乮NQ乯偼侽偵側傝傑偡丅偙偺侽偑俀抂巕偵擖傝傑偡偐傜丄侾抂巕偑侽偺側偭偰傕Q偼侾傪曐帩偟傑偡丅

幚尡夞楬

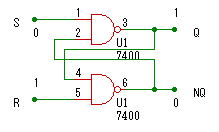

S偲R偵墴偟儃僞儞僗僀僢僠丄Q偵LED傪愙懕偡傟偽丄婰壇夞楬偺摦嶌偺妋擣偑偱偒傑偡丅偙偺夞楬偼儔僢僠乮latch丗偐傫偸偒乯夞楬偲傕屇偽傟傑偡丅

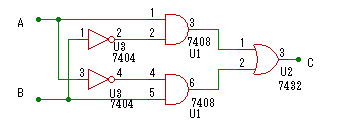

EXOR墘嶼

丂EXOR墘嶼偼丄攔懠揑榑棟榓偲傕屇偽傟傑偡丅榑棟幃偱偼

丂C = ~A丒B + A丒 ~B

偱丄偦偪傜偐堦曽偺傒偑侾偺帪丄弌椡偑侾偲側傝傑偡丅OR偲堎側傝丄嫟偵侾偺偲偒偼侽偵側傝傑偡乮偙傟偑攔懠揑榑棟榓偲屇偽傟傞強埲偱偡乯丅

僋儕傾

偙偺夞楬偼忋壓懳徾偱偡偐傜丄S=1偺傑傑丄R傪侽偵偡傞偲NQ偑侾偵側傝丄Q偼0偵側傝傑偡丅R傪侾偵栠偟偰傕丄Q偼侽偺傑傑偱偡丅

丂寢嬊丄堦弖 S=0丂偵偡傞偲Q=1偲側傝丄R=0 偵偡傞偲丄Q=0 偵僋儕傾偝傟傑偡丅

僼傿乕僪僶僢僋

偙偺夞楬偺摿挜偼丄弌椡Q偑壓偺NAND僎乕僩傪捠夁屻Q偺擖椡偵栠偭偰偄傞偙偲偱偡丅偙偺傛偆偵丄弌椡傪擖椡偵栠偡偙偲偱婰壇傪偡傞偙偲偑偱偒傑偡丅偙偺傛偆側夞楬傪僼傿乕僪僶僢僋夞楬偲偄偄傑偡丅

墳梡夞楬

仭儗僕僗僞

丂偙偺婰壇夞楬傪8屄懇偹傞偲8價僢僩乮1僶僀僩乯偺婰壇夞楬乮儗僕僗僞乯偑崌惉偱偒傑偡丅

仭壩嵭曬抦婍

S儃僞儞傪墴偡偲丄僽僓乕偑柭傝弌偟傑偡丅婰壇乮儔僢僠乯夞楬偵側偭偰偄傟偽丄儃僞儞傪棧偟偰傕側傝懕偗傑偡丅

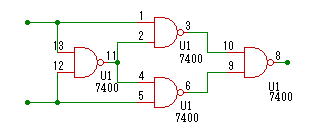

NAND慺巕偱崌惉

摨偠夞楬傪丄AND偟偨屻偵NOT傪偟偰偐傜弌椡偡傞慺巕 NAND 傪棙梡偡傞偲丄偙偺慺巕偩偗偱丄摨偠摦嶌傪偡傞夞楬偑偱偒傑偡丅堦偮偺IC偺撪晹偺4屄偺慺巕傪偡傋偰棙梡偟偰偄傑偡丅

夞楬偺慻傒崌傢偣

EXOR傪偦偺傑傑丄AND偲OR偲NOT慺巕偱崌惉偡傞偲師偺傛偆偵側傝傑偡丅3庬偺榑棟墘嶼傪棙梡偡傞偨傔丄AND偲OR偲NOT偺3屄偺IC偑昁梫偱偡丅

帺摦榑棟崌惉

丂榑棟幃傪擖椡偡傞偲丄偦傟傪幚尰偡傞嵟揔偵嬤偄夞楬傪帺摦惗惉偡傞僔僗僥儉偑棙梡偱偒傑偡丅傑偨丅FPGA傗CPLD傪棙梡偡傞偲丄堦偮偺IC偺撪晹偺悢昐偐傜悢枩偺慺巕偑偁傝丄擖椡尵岅乮HDL乯偐傜丄昁梫側榑棟傪帺摦崌惉偟偰偔傟傑偡丅偟偨偑偭偰丄榑棟幃儗儀儖偺娙扨壔傪恖庤偱峴偆昁梫惈偼彮側偔側偭偰偄傑偡丅